CCM-BOOGIE

3U, High Performance Dual Core CompactPCI ® CPU Board

The CCM-BOOGIE is a versatile 4HP/3U CompactPCI® CPU board, equipped with an Intel® Core™ 2 Duo processor at up to 2.26GHz clock, and up to 6GB dual channel capable DDR3 RAM. Four native 3Gbps RAID capable Serial ATA channels are available for mass storage I/O, and in addition another two from a secondary RAID controller. The CCM-BOOGIE has been designed especially for systems which require dual core high performance at moderate power consumption.

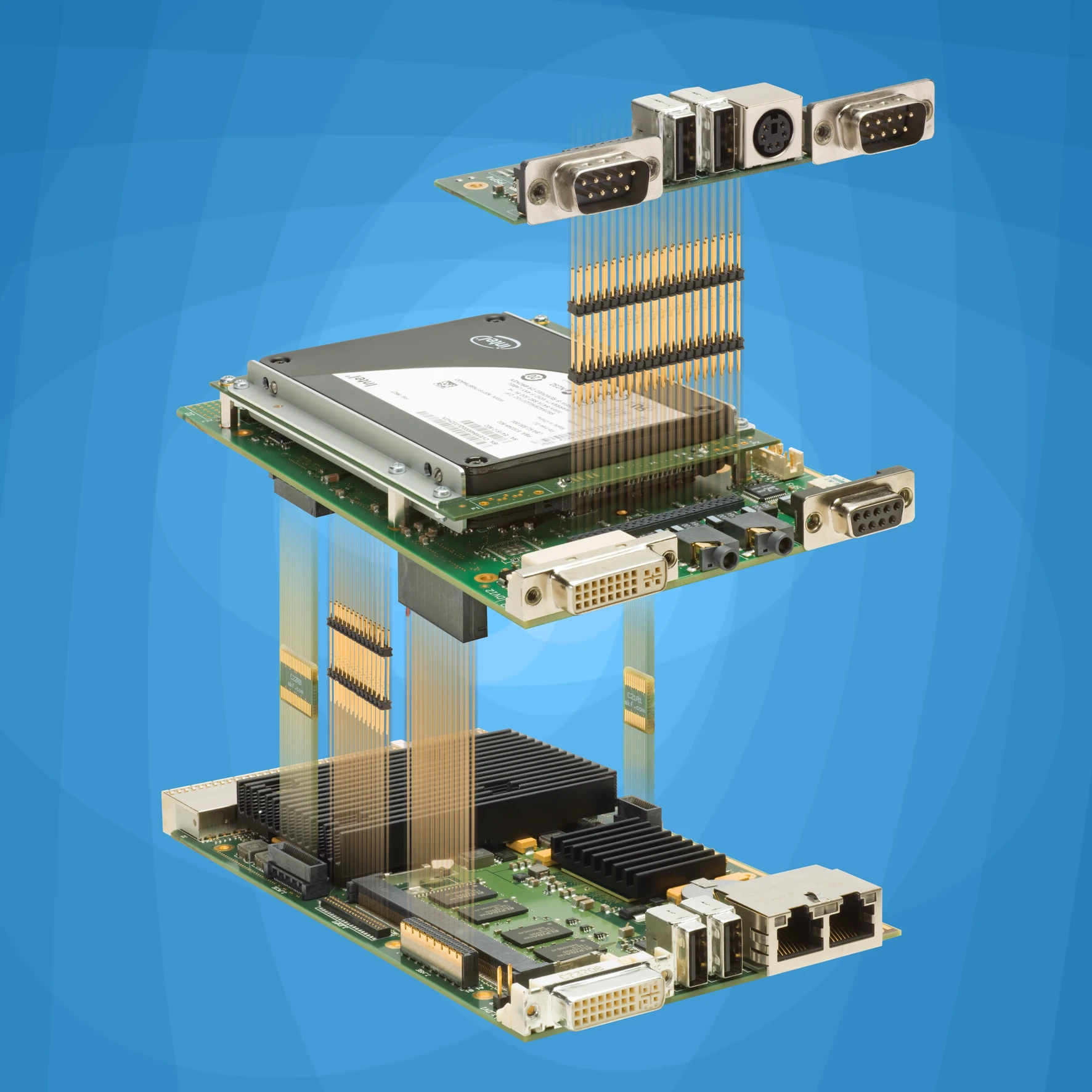

The CCM-BOOGIE is provided with a high performance mobile chipset (Intel® GS45) which operates at up to 1066MHz FSB and up to 1066MHz DDR3 memory clock for optimum system throughput. The chipset is based on PCI Express® technology and has a powerful integrated graphics accelerator. The DVI-I front panel connector enables dual screen video operation. Two Gigabit Ethernet controllers are provided for high speed connectivity (one of them IEEE 802.1as TimeSync compliant). The CCM-BOOGIE is equipped wit a set of local expansion interface connectors, which can be optionally used to directly attach a suitable (application specific) mezzanine side board, e.g. for audio- and legacy support, PCI Express based I/O circuitry, and a secondary DVI video output. Carrier board and side card come as a readily assembled 8HP unit typically. Most mezzanine cards can accommodate in addition a 2.5-inch drive. Also as an option, a suitable rear I/O transition module is available to the CCM-BOOGIE.

As a popular add-on option, the CCM-BOOGIE can be delivered with a small mezzanine module (C42-SATA), which accommodates a 1.8-inch SATA solid state drive (SSD). Alternatively, the C40-SCFA mezzanine card is provided with an industrial grade CompactFlash memory card, and/or an even more rugged USB Silicon State Drive (SSD). Both mezzanine modules fit into the 4HP envelope of the entire assembly.

Downloads & Ressources

Documents

General Information

Firmware

Drivers

Suitable Carrier Cards

Specifications

- Single size CompactPCI style Eurocard (160x100mm2), front panel width 4HP (20.3mm)

Simplified Block Diagram